## **DESCRIPTION**

The AD8837 of devices provides an integrated motor driver solution for cameras, consumer products, toys, and other low-voltage or battery-powered motion control applications. The device can drive one dc motor or other devices like solenoids. The output driver block consists of N-channel power MOSFETs, Stop, Forward, Reverse and Brake Functions.

The AD8837 of devices can supply 1.8 A of maximum output current, 3.5A of peak current. It operates on a motor power supply voltage from 0 to 11V, and a device power supply voltage of 1.8V to 7V.

The AD8837 device has a PWM (IN1-IN2) input interface.

Internal shutdown functions are provided for overcurrent protection, short-circuit protection, undervoltage lockout, and overtemperature.

The AD8837 is available DFN8 (2x2) package.

## ORDERING INFORMATION

| Package Type                   | Part Number             |            |  |

|--------------------------------|-------------------------|------------|--|

| DFN8(2x2)                      | J8                      | AD8837J8R  |  |

| SPQ: 3,000pcs/Reel             | 30                      | AD8837J8VR |  |

| Note                           | V: Halogen free Package |            |  |

| Note                           | R: Tape & Reel          |            |  |

| AiT provides all RoHS products |                         |            |  |

## **FEATURES**

- H-Bridge Motor Driver

- Drives a DC Motor or Other Loads

- Low MOSFET On-Resistance: HS + LS 330 mΩ

- 1.8A Maximum Drive Current, 3.5A Peak Current

- Separate Motor and Logic Supply Pins:

- Motor V<sub>M</sub>: 0 to 11V

- Logic Vcc: 1.8 to 7 V

- PWM or PH-EN Interface

- PWM, IN1 and IN2

- Low Iq: typ. 120 nA

- Protection Features

- V<sub>CC</sub> Undervoltage Lockout (UVLO)

- Overcurrent Protection (OCP)

- Thermal Shutdown (TSD)

- Available in DFN8 (2x2) package

## **APPLICATION**

- Cameras

- DSLR Lenses

- Consumer Products

- Toys

- Robotics

- Medical Devices

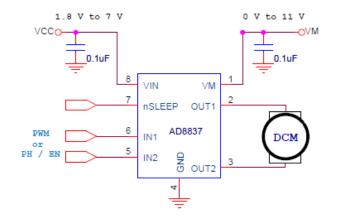

## TYPICAL APPLICATION

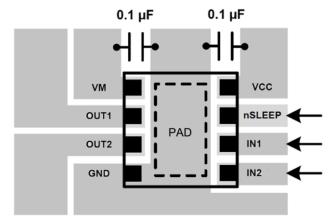

# PIN DESCRIPTION

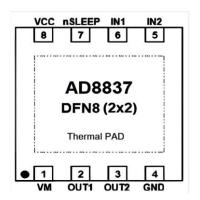

DFN8(2x2), J8 Top View

| Pin #<br>DFN8(2x2) | Symbol         | Туре | Function                                                                                                                                                                                          |

|--------------------|----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                  | VM             | PWR  | Motor Supply Voltage  Bypass this pin to the GND with a 0.1µF ceramic capacitor.                                                                                                                  |

| 2                  | OUT1           | 0    | Motor Output 1 Connect these pins to the motor winding.                                                                                                                                           |

| 3                  | OUT2           | 0    | Motor Output 2 Connect these pins to the motor winding.                                                                                                                                           |

| 4                  | GND            | PWR  | Device ground. This pin must be connected to ground                                                                                                                                               |

| 5                  | IN2            | I    | Input logic 2                                                                                                                                                                                     |

| 6                  | IN1            | I    | Input logic 1                                                                                                                                                                                     |

| 7                  | nSLEEP         | I    | The Sleep mode pin includes an internal pull-down resistor.  A logic Low on this pin forces the device into low-power Sleep mode, while a logic High allows the device to operate in normal mode. |

| 8                  | Vcc            | PWR  | Logic power supply Bypass this pin to the GND with a 0.1µF ceramic capacitor.                                                                                                                     |

| -                  | Thermal<br>PAD | PWR  | Exposed pad (heatsink) - connects to ground for proper thermal dissipation.                                                                                                                       |

# **ABSOLUTE MAXIMUM RATINGS**

| V <sub>M</sub> , Motor Power-Supply Voltage   | -0.3V ~ 12V        |

|-----------------------------------------------|--------------------|

| Vcc, Logic Power Supply Voltage               | -0.3V ~ 7V         |

| V <sub>IN,</sub> IN1, IN2 Input Logic Voltage | -0.5V ~7V          |

| Iouт, OUT1, OUT2 Peak Drive Current           | Internally Limited |

| T <sub>J</sub> , Junction Temperature         | -40°C ~ +150°C     |

| T <sub>A</sub> , Environment Temperature      | -40°C ~ +85°C      |

| T <sub>STG</sub> , Storage Temperature        | -55°C~+150°C       |

| T <sub>L</sub> , Lead Pin Temperature         | +300°C             |

Stress beyond above listed "Absolute Maximum Ratings" may lead permanent damage to the device. These are stress ratings only and operations of the device at these or any other conditions beyond those indicated in the operational sections of the specifications are not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **ELECTRICAL CHARACTERISTICS**

$T_A$  = 25°C,  $V_{BB}$  = 24V ,  $C_L$ =1nF ,unless otherwise specified.

| Parameter                         | Symbol            | Conditions                               | Min. | Тур. | Max. | Unit |

|-----------------------------------|-------------------|------------------------------------------|------|------|------|------|

| REGULAR PARAMETERS                |                   |                                          |      |      |      |      |

| Logic Power Supply Voltage        | Vcc               |                                          | 1.8  | -    | 7    | V    |

| Motor Power Supply Voltage        | V <sub>M</sub>    |                                          | 0    | -    | 11   | V    |

|                                   |                   | V <sub>M</sub> =5V, V <sub>CC</sub> =3V, |      | 50   | 400  |      |

| V. O                              |                   | fpwm = 0                                 | -    | 50   | 100  | μA   |

| V <sub>M</sub> Operating Current  | I <sub>∨M</sub>   | V <sub>M</sub> =5V, V <sub>CC</sub> =3V, |      | 0.3  | 1.2  | mA   |

|                                   |                   | fpwm = 50 kHz                            | -    |      |      |      |

| V. Osissasat Osmant               | I <sub>VM-Q</sub> | V <sub>M</sub> =5V, V <sub>CC</sub> =3V, | -    | 30   | 95   | nA   |

| V <sub>M</sub> Quiescent Current  |                   | nSLEEP = 0                               |      |      |      |      |

|                                   | lcc               | V <sub>M</sub> =5V, V <sub>CC</sub> =3V, | -    | 250  | 450  | μА   |

| V 0                               |                   | fpwm = 0                                 |      |      |      |      |

| Vcc Operating Current             |                   | V <sub>M</sub> =5V, V <sub>CC</sub> =3V, |      | 0.35 | 1.20 |      |

|                                   |                   | fрwм = 50 kHz                            | -    |      |      | mA   |

| V Ovices and Comment              |                   | V <sub>M</sub> =5V, V <sub>CC</sub> =3V, |      | 5    | 25   | ^    |

| V <sub>CC</sub> Quiescent Current | I <sub>CC-Q</sub> | nSLEEP = 0                               | -    |      |      | nA   |

| Parameter                   | Symbol                | Conditions                                                                               | Min.     | Тур.                 | Max.                | Unit |

|-----------------------------|-----------------------|------------------------------------------------------------------------------------------|----------|----------------------|---------------------|------|

| MOTOR DRIVER OUTPUT         |                       |                                                                                          |          |                      |                     |      |

| HS + LS FET On-Resistance   | R <sub>DS(ON)</sub>   | I <sub>OUT</sub> =800mA, V <sub>M</sub> =5,<br>V <sub>CC</sub> =3V, T <sub>J</sub> =25°C | -        | 0.33                 | 0.38                | Ω    |

| Off-State Leakage Current   | loff                  | V <sub>OUT</sub> =0                                                                      | -200     | -                    | 200                 | nA   |

| CONTROL INPUTS (IN1/IN2)    |                       |                                                                                          |          |                      |                     |      |

| High Level Input Voltage    | VINH                  |                                                                                          | -        | 0.46xV <sub>CC</sub> | 0.5xV <sub>CC</sub> |      |

| Low Level Input Voltage     | V <sub>INL</sub>      |                                                                                          | 0.25xVcc | 0.38xVcc             | -                   | V    |

| Logic Input Hysteresis      | V <sub>HYS</sub>      |                                                                                          | -        | 0.08xV <sub>CC</sub> | -                   |      |

| High Level Input Current    | linh                  | V <sub>IN</sub> =3.3V                                                                    | -        | -                    | 50                  |      |

| Low Level Input Current     | I <sub>INL</sub>      | V <sub>IN</sub> =0V                                                                      | -5       | -                    | 5                   | μA   |

| Pulldown Resistance         | R <sub>PD</sub>       |                                                                                          | -        | 100                  | -                   | ΚΩ   |

| Pulldown Resistance         |                       | nSLEEP                                                                                   | -        | 55                   | -                   |      |

| PROTECTION CIRCUITS         |                       |                                                                                          |          |                      |                     |      |

| Vcc Undervoltage Lockout    | $V_{UVLO_{-R}}$       | V <sub>BB</sub> Increasing                                                               | -        | -                    | 1.7                 | V    |

| Vcc Undervoltage Lockout    |                       |                                                                                          |          | 0.1                  | _                   | mV   |

| Hysteresis                  | V <sub>UVLO_HYS</sub> |                                                                                          | -        | 0.1                  | _                   | IIIV |

| Overcurrent Protection Trip | locp                  |                                                                                          | 1.9      | _                    | 3.5                 | А    |

| Level                       |                       |                                                                                          |          |                      |                     |      |

| Overcurrent Protection      | <b>t</b> DEG          |                                                                                          | -        | 1                    | -                   | μs   |

| Filter Burr Time            |                       |                                                                                          |          |                      |                     | -    |

| Overcurrent Retry Time      | t <sub>RETRY</sub>    |                                                                                          | -        | 1                    | -                   | ms   |

| Thermal Shutdown            | $T_TSD$               | Temperature                                                                              | 150      | 160                  | 180                 | °C   |

| Temperature                 | 1130                  | increasing                                                                               | 100      |                      |                     |      |

| Thermal Shutdown            | T <sub>TSD</sub> -HYS | Recovery =                                                                               | _        | 15                   | _                   | °C   |

| Hysteresis                  | i Ion-Hio             | TJTSD — TTSDhys                                                                          | _        | 10                   | _                   | J    |

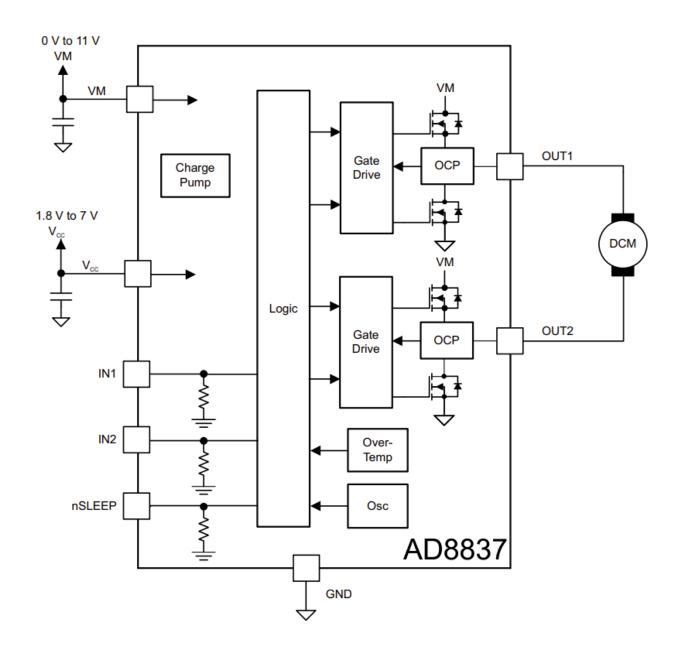

# **BLOCK DIAGRAM**

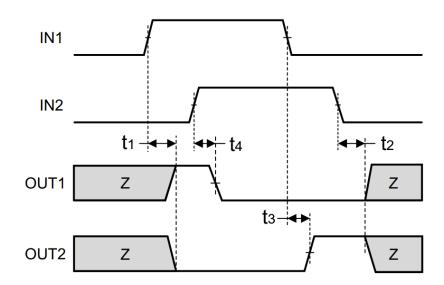

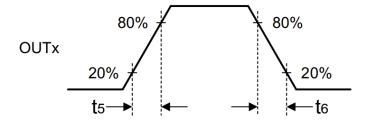

# TIMING REQUIREMENTS

$V_{CC}$ =3V,  $V_{M}$ =5V,  $T_{A}$ =25 $^{\circ}$ C,  $R_{LOAD}$ =20 $\Omega$

| Time           | Parameter                                                | Max      | Unit |

|----------------|----------------------------------------------------------|----------|------|

| t <sub>1</sub> | Output enable time                                       | 300      | ns   |

| t <sub>2</sub> | Output disable time                                      | 300      | ns   |

| t <sub>3</sub> | Delay time, INx high to OUTx high                        | 160      | ns   |

| t <sub>4</sub> | Delay time, INx low to OUTx low                          | 160      | ns   |

| t <sub>5</sub> | Output rise time                                         | 30 ~ 188 | ns   |

| t <sub>6</sub> | Output fall time                                         | 30 ~ 188 | ns   |

|                | Wake-up Delay, Time from nSLEEP rising edge to IC normal | 30       | μs   |

|                | operation                                                |          |      |

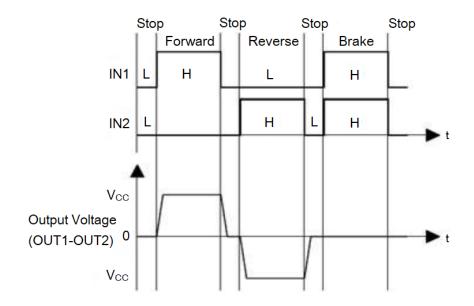

# **INPUT-OUTPUT LOGIC TABLE**

| nSLEEP | IN1 | IN2 | OUT1 | OUT2 | Function          |

|--------|-----|-----|------|------|-------------------|

| L      | Х   | Х   | Hi-Z | Hi-Z | Coasting          |

| Н      | L   | L   | Hi-Z | Hi-Z | Coasting          |

| Н      | L   | Н   | L    | Н    | Reverse           |

| Н      | Н   | L   | Н    | L    | Forward           |

| Н      | Ш   | ш   |      | -    | Brake (Slow Decay |

|        | Н   | Н   | L    | L    | Operation)        |

# **INPUT-OUTPUT WAVEFORM**

**LOW-VOLTAGE H-BRIDGE DRIVER**

# **Function Description**

#### Overview

The AD8837 is an H-bridge driver capable of driving a DC motor or other devices such as solenoids. The outputs are controlled via the PWM inputs IN1 and IN2.

The device features a low-power Sleep mode, which can be enabled using the nSLEEP pin.

The AD8837 integrates both the FET drivers and the FET control circuitry, significantly reducing the number of external components required for a motor driver system. In addition, the device includes several protection features, such as undervoltage lockout (UVLO), overcurrent protection (OCP), and thermal shutdown (TSD).

#### **Low-Power Sleep Mode**

When the nSLEEP pin is driven Low, the AD8837 enters a low-power Sleep mode. In this state, all non-essential internal circuits are disabled, minimizing power consumption.

#### **Power and Input Pins**

- The input pins can be driven within the recommended operating range regardless of the presence of V<sub>CC</sub> or V<sub>M</sub>. No leakage paths exist when the power supply is absent.

- Each input pin includes a weak internal pull-down resistor ( $\sim$ 100 k $\Omega$ ) to GND.

- V<sub>CC</sub> and V<sub>M</sub> can be powered on or off in any sequence.

- When Vcc is turned off, the device enters a low-power state and draws minimal current from Vм.

- Logic supply voltage can range from 1.8V to 7V; in this case, V<sub>CC</sub> and V<sub>M</sub> can be tied together.

- V<sub>M</sub> does not have undervoltage lockout (UVLO); as long as V<sub>CC</sub> > 1.8V, the internal logic remains active.

- $V_M$  voltage may drop to 0 V, but the load may not be fully driven at low  $V_M$  voltage.

## Vcc Undervoltage Lockout (UVLO)

- If Vcc falls below the UVLO threshold, all FETs in the H-bridge are disabled.

- Normal operation resumes once Vcc rises above the UVLO threshold.

# **Overcurrent Protection (OCP)**

- Each FET includes an analog current limit circuit that restricts current by disabling the gate driver.

- If the analog current limit persists beyond t<sub>DEG</sub> (~1 μs), all H-bridge FETs are disabled and automatically recover after a delay t<sub>OCP</sub>.

- Overcurrent is detected on both high-side and low-side FETs.

- Conditions triggering overcurrent protection include:

- Short to V<sub>M</sub> or GND

- Short from OUT1 to OUT2

#### Thermal Shutdown (TSD)

- If the junction temperature (TJ) exceeds the safe limit, all FETs in the H-bridge are disabled.

- Normal operation automatically resumes when the temperature drops back to a safe level.

### **Fault Conditions Summary**

| Fault Condition              | Trigger Condition              | H-Bridge State | Recovery Condition     |

|------------------------------|--------------------------------|----------------|------------------------|

| Vcc Undervoltage (UVLO)      | V <sub>CC</sub> < 1.7V         | All FETs off   | V <sub>CC</sub> >1.8V  |

| Overcurrent Protection (OCP) | I <sub>OUT</sub> > 1.9 A (min) | All FETs off   | After tretry           |

| Thermal Shutdown (TSD)       | T <sub>J</sub> > 150°C (min)   | All FETs off   | T <sub>J</sub> > 140°C |

## **Device Operating Modes**

- Normal Operation: Unless the nSLEEP pin is driven Low, the AD8837 operates in normal mode.

- Sleep Mode: When nSLEEP = Low, the device enters low-power Sleep mode, and all H-bridge FETs are disabled (Hi-Z state). When nSLEEP is driven High, the device automatically exits Sleep mode.

- Fault Mode: During UVLO (V<sub>CC</sub> undervoltage), OCP (overcurrent), or TSD (thermal shutdown) events, the H-bridge outputs are disabled. Normal operation resumes once the fault condition is cleared.

| Operating Mode   | Condition      | H-Bridge     | Notes                                         |

|------------------|----------------|--------------|-----------------------------------------------|

|                  |                | State        |                                               |

| Normal Operation | nSLEEP = High  | Driving      | _                                             |

| Sleep Mode       | nSLEEP = Low   | All FETs off | H-bridge outputs in Hi-Z                      |

| Fault Mode       | UVLO, OCP, TSD | All FETs off | Outputs remain off until the fault is cleared |

### **Typical Operating Conditions**

| Parameter            | Symbol         | Example Value | Unit |

|----------------------|----------------|---------------|------|

| Motor Supply Voltage | V <sub>M</sub> | 9             | V    |

| Logic Supply Voltage | Vcc            | 3.3           | V    |

| Output Drive Current | Іоит           | 800           | mA   |

### **Device Power Dissipation**

The power dissipation of the AD8837 is primarily determined by the on-resistance of the output FETs (R<sub>DS(ON)</sub>). The approximate average power dissipation during motor operation can be calculated as:

$P_{TOT}=R_{DS(ON)}\times (I_{OUT(RMS)})^2$

### Where:

- P<sub>TOT</sub> = Total power dissipation of the device

- R<sub>DS(ON)</sub> = Sum of the on-resistances of the high-side and low-side FETs

- I<sub>OUT(RMS)</sub> = RMS or DC current delivered to the load.

The maximum allowable power dissipation depends on the ambient temperature and thermal management. Note that R<sub>DS(ON)</sub> increases with temperature, so device power dissipation rises as the chip heats up.

The AD8837 features thermal shutdown protection (TSD). If the junction temperature exceeds approximately 150°C, the H-bridge FETs are disabled until the temperature drops back to a safe level. Thermal shutdown indicates excessive power dissipation, insufficient cooling, or high ambient temperature.

## **Recommended Operating Power Supply**

• Power-On Sequence:

$V_{CC}$  and  $V_{M}$  can be powered on or off in any sequence. When  $V_{CC}$  is turned off, the device enters a low-power state, drawing minimal current from  $V_{M}$ .

Logic Supply Voltage:

When the logic supply voltage is between 1.8 V and 7 V,  $V_{CC}$  and  $V_{M}$  can be connected together.

- Bypass Capacitors:

- Connect 0.1  $\mu$ F ceramic capacitors from  $V_M$  and  $V_{CC}$  to GND. Place these capacitors as close as possible to the  $V_M$  and  $V_{CC}$  pins.

- V<sub>M</sub> Undervoltage Note:

The  $V_M$  supply does not have undervoltage lockout (UVLO); as long as  $V_{CC} > 1.8$  V, the internal logic remains active.

Note: V<sub>M</sub> may drop to 0 V under certain conditions, but the load may not be fully driven if V<sub>M</sub> voltage is too low.

#### **Layout Guidelines**

- Bypass Capacitors: Use low-impedance ceramic capacitors (recommended 0.1 μF) between V<sub>M</sub>/V<sub>CC</sub> and GND.

- Placement: Place these capacitors as close as possible to the  $V_M$  and  $V_{CC}$  pins.

- Grounding: Connect the capacitors to the device GND pin using wide traces or a ground plane to ensure proper decoupling and minimize voltage drops.

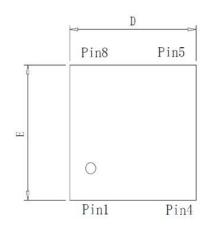

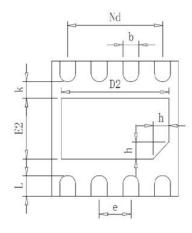

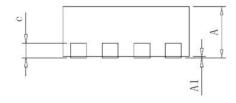

# **PACKAGE INFORMATION**

Dimension in DFN8(2x2) (Unit: mm)

Top View

Side View

**Bottom View**

| Symbol | Min       | Max   |  |  |

|--------|-----------|-------|--|--|

| Α      | 0.700     | 0.800 |  |  |

| A1     | 0.000     | 0.050 |  |  |

| b      | 0.200     | 0.300 |  |  |

| С      | 0.203     | BREF  |  |  |

| D      | 1.900     | 2.100 |  |  |

| D2     | 1.600     | 1.800 |  |  |

| Nd     | 1.500 BSC |       |  |  |

| е      | 0.500     | BSC   |  |  |

| E      | 1.900     | 2.100 |  |  |

| E2     | 0.800     | 1.000 |  |  |

| h      | 0.200     | 0.300 |  |  |

| k      | 0.200     | 0.300 |  |  |

| L      | 0.250     | 0.350 |  |  |

# **IMPORTANT NOTICE**

AiT Semiconductor Inc. (AiT) reserves the right to make changes to any its product, specifications, to discontinue any integrated circuit product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

AiT Semiconductor Inc.'s integrated circuit products are not designed, intended, authorized, or warranted to be suitable for use in life support applications, devices or systems or other critical applications. Use of AiT products in such applications is understood to be fully at the risk of the customer. As used herein may involve potential risks of death, personal injury, or servere property, or environmental damage. In order to minimize risks associated with the customer's applications, the customer should provide adequate design and operating safeguards.

AiT Semiconductor Inc. assumes to no liability to customer product design or application support. AiT warrants the performance of its products of the specifications applicable at the time of sale.