### **DESCRIPTION**

The A93C46 (1K Bit) is Electrically Erasable Programmable Memory (EEPROM) devices accessed through the MICROWIRE™ bus protocol. The memory arrays can be configured either in bytes (x8b) or in words (x16b).

The device is optimized for use in many industrial and commercial applications where low-power and low-voltage operation is essential.

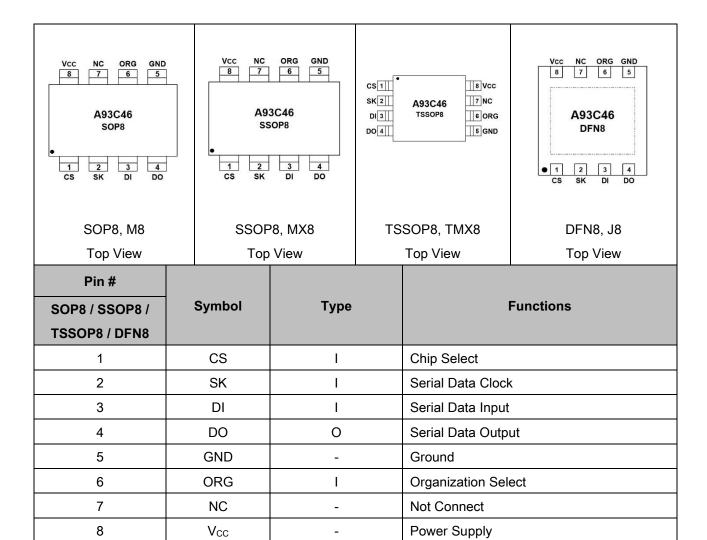

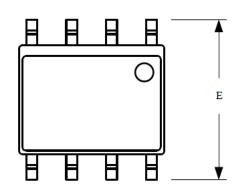

The A93C46 is available in SOP8, SSOP8, TSSOP8 and DFN8 Packages.

### **FEATURES**

- Industry Standard MICROWIRE™ Bus

- Low-Voltage Operation: V<sub>CC</sub> = 1.7V to 5.5V

- Dual Organization: by word (x16) or byte (x8)

- Programming Instructions Byte, Word or Entire Memory

- Sequential Read Operation.

- 2 MHz Clock Rate (5V)

- Self-Timed Write Cycle within 3ms Maximum.

- High Reliability:

Endurance: 4,000,000 Write Cycles

Data Retention: 100 Years

Available in SOP8, SSOP8, TSSOP8 and DFN8 Packages

### ORDERING INFORMATION

| Package Type                   |                      | Part Number   | r              |  |

|--------------------------------|----------------------|---------------|----------------|--|

| 0000                           |                      | A93C46M8R-A   | A93C46M8VR-A   |  |

| SOP8                           | M8                   |               | A93C46M8VR-B   |  |

| SPQ:2,500pcs/Reel              |                      |               | A93C46M8VR-C   |  |

| 00000                          |                      | A93C46MX8R-A  | A93C46MX8VR-A  |  |

| SSOP8                          | MX8                  |               | A93C46MX8VR-B  |  |

| SPQ:3,000pcs/Reel              |                      |               | A93C46MX8VR-C  |  |

| TOCODO                         |                      | A93C46TMX8R-A | A93C46TMX8VR-A |  |

| TSSOP8                         | TMX8                 |               | A93C46TMX8VR-B |  |

| SPQ: 3,000pcs/Reel             |                      |               | A93C46TMX8VR-C |  |

| DEMO                           |                      | A93C46J8R-A   | A93C46J8VR-A   |  |

| DFN8                           | J8                   |               | A93C46J8VR-B   |  |

| SPQ: 3,000pcs/Reel             |                      |               | A93C46J8VR-C   |  |

|                                | Temperature          | :             |                |  |

|                                | A:-40°C to           | +85°C         |                |  |

| Note                           | B: -40°C to          | +105°C        |                |  |

| Note                           | C : -40°C to +125°C: |               |                |  |

|                                | V :Halogen F         | Free Package  |                |  |

|                                | R : Tape & Reel      |               |                |  |

| AiT provides all RoHS products |                      |               |                |  |

REV0.9 - AUG 2024 RELEASED - -1

## **PIN DESCIPTION**

## **ABSOLUTE MAXIMUM RATINGS**

| Ambient Operating Temperature | -40°C ~ +130°C                |

|-------------------------------|-------------------------------|

| Storage Temperature           | -65°C ~ +150°C                |

| DC Supply Voltage             | -0.3V ~ 6.5V                  |

| Input / Output Voltage        | -0.3V ~ V <sub>CC</sub> +0.3V |

| Electrostatic Pulse (HBM)     | 4000V                         |

| Electrostatic Pulse (MM)      | 250V                          |

| Electrostatic Pulse (CDM)     | 2000V                         |

Stresses above may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the Electrical Characteristics is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

REV0.9 - AUG 2024 RELEASED - - 2 -

# RELIABILITY CHARACTERISTICS

Applicable over recommended operating range from  $T_A$  = 25°C, f = 1.0 MHz,  $V_{CC}$  = +5.0V

| Parameter                | Symbol | Min. | Тур. | Max. | Unit |

|--------------------------|--------|------|------|------|------|

| Input/Output Capacitance | Cı/o   | -    | -    | 8    | pF   |

| Input Capacitance        | Cin    | -    | -    | 6    | pF   |

### DC ELECTRICAL CHARACTERISTICS

$T_A = 25$ °C, f = 1.0 MHz,  $V_{CC} = +5.0$ V, unless otherwise specified

| Parameter                        | Symbol               | Conditio | Min.      | Тур. | Max.                  | Unit |

|----------------------------------|----------------------|----------|-----------|------|-----------------------|------|

|                                  |                      | n        |           |      |                       |      |

| Supply Voltage                   | Vcc                  | -        | 1.8       | 1    | 5.5                   | V    |

| Input Leakage Current            | ILI                  | -        | -         | -    | ±2.5                  | μΑ   |

| Output Leakage Current           | I <sub>LO</sub>      | -        | -         | 1    | ±2.5                  | μΑ   |

| Operating Supply Current (Read)  | I <sub>CC-Read</sub> | -        | -         | 0.5  | 2.0                   | mA   |

| Operating Supply Current (Write) | ICC-Write            | -        | -         | 2.0  | 3.0                   | mA   |

| Standby Supply Current           | I <sub>SB2</sub> *   | -        | -         | 0.1  | 5.0                   | μΑ   |

| Input Low Level                  | V <sub>IL</sub>      | -        | -0.3      | ı    | V <sub>CC</sub> x 0.3 | V    |

| Input High Level                 | ViH                  | -        | Vcc x 0.7 | ı    | V <sub>CC</sub> + 0.3 | V    |

| Output Low Level                 | V <sub>OH</sub>      | -        | -         | ı    | 0.2                   | V    |

| Output High Level                | Voh                  | -        | Vcc x 0.7 | -    | -                     | V    |

# **AC ELECTRICAL CHARACTERISTICS**

$T_A$  = 25°C, f = 1.0 MHz,  $V_{CC}$  = +5.0V, unless otherwise specified.

| Parameter                           | Symbol           | Conditio | Min. | Тур. | Max. | Unit        |

|-------------------------------------|------------------|----------|------|------|------|-------------|

|                                     |                  | n        |      |      |      |             |

| Clock Frequency                     | fsĸ              | -        | DC   | -    | 2    | MHz         |

| Chip Select Low to Clock High       | -                | 1        | 50   | -    | -    | ns          |

| Chip Select Setup Time              | tcss             | -        | 50   | -    | -    | ns          |

| Chip Select Low to Chip Select High | tcs              | 1        | 200  | -    | -    | ns          |

| Clock High Time                     | tsкн             | ı        | 200  | -    | -    | ns          |

| Clock Low Time                      | <b>t</b> skl     | -        | 200  | -    | -    | ns          |

| Data In Setup Time                  | t <sub>DIS</sub> | -        | 50   | -    | -    | ns          |

| Data In Hold Time                   | <b>t</b> DIH     | -        | 50   | -    | -    | ns          |

| Clock Setup Time (Relative To S)    | tsks             | -        | 50   | -    | -    | ns          |

| Chip Select Hold Time               | tсsн             | -        | 0    | -    | -    | ns          |

| Chip Select to READ/BUSY Status     | tsv              | -        | -    | -    | 200  | ns          |

| Chip Select Low to Output Hi-Z      | <b>t</b> DF      | -        | -    | -    | 100  | ns          |

| Delay to Output Low                 | t <sub>PD0</sub> | -        | -    | -    | 200  | μs          |

| Delay to Output Valid               | t <sub>PD1</sub> | -        | -    | -    | 200  | ns          |

| Erase or Write Cycle Time           | twp              | -        | -    | -    | 3    | ms          |

| Write Cycle Endurance               |                  | -        | 4M   | -    | -    | Write Cycle |

REV0.9 - AUG 2024 RELEASED - - 3 -

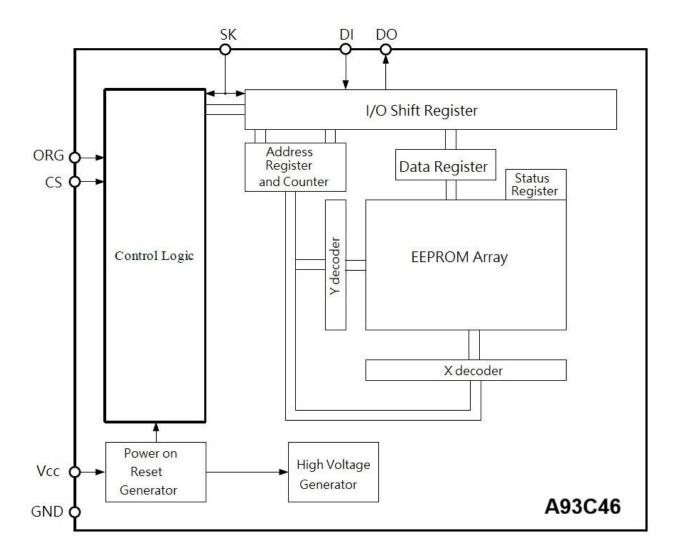

# **BLOCK DIAGRAM**

REV0.9 - AUG 2024 RELEASED - - 4

### **DETAILED INFORMATION**

**Chip Select (CS):** The Chip Select (CS) pin is used to control device selection. The A93C46 is selected when the CS pin is high. When the device is not selected, data will not be accepted via the Serial Data Input (DI) pin, and the Serial Output (DO) pin will remain in a high-impedance state.

**Serial Data Clock (SK):** The Serial Data Clock (SK) pin is used to synchronize the communication between a master and the A93C46. Instructions, addresses or data present on the Serial Data Input (DI) pin is latched in on the rising edge of SK, while output on the Serial Data Output (DO) pin is also clocked out on the rising edge of SK.

**Serial Data Input (DI)**: The Serial Data Input (DI) pin is used to transfer data into the device. It receives instructions, addresses and data. Data is latched on the rising edge of the Serial Data Clock (SK).

**Serial Data Output (DO)**: The Serial Data Output (DO) pin is used to transfer data out of the A93C46. During a read sequence, data is shifted out on this pin after the rising edge of the Serial Data Clock (SK). This pin also outputs the Ready/Busy status of the part if CS is brought high after being low for a minimum of tcs and an erase or write operation has been initiated.

**Ground (GND)**: The ground reference for the power supply. The Ground (GND) pin should be connected to the system ground.

Internal Organization (ORG): The Internal Organization (ORG) pin is used to select between the x16 or x8 memory organizations of the device. When the ORG pin is tied to  $V_{CC}$ , the x16 memory organization is selected. When the ORG pin is tied to GND, the x8 memory organization is selected. If the ORG pin is left unconnected and the application does not load the input beyond the capability of the internal  $1M\Omega$  pull-up resistor, then the x16 organization is selected.

**Device Power Supply (Vcc)**: The Device Power Supply (Vcc) pin is used to supply the source voltage to the device. Operations at invalid Vcc voltages may produce spurious results and should not be attempted.

REV0.9 - AUG 2024 RELEASED - - 5 -

### **FUNCTION DESCRIPTION**

#### 1. Memory Organization

The A93C46 is Electrically Erasable Programmable Memory (EEPROM) devices accessed through the MICROWIRE™ bus protocol. The memory array can be configured either in bytes (x8b) or in words (x16b).

The A93C46 memory is organized either as bytes (x8) or as words (x16). If Organization Select (ORG) is unconnected (or connected to  $V_{CC}$ ) the x16 organization is selected; when Organization Select (ORG) is connected to Ground the x8 organization is selected. When the A93C46 is in Standby mode, Organization Select (ORG) should be set either to GND or  $V_{CC}$  to reach the device minimum power consumption (as any voltage between GND and  $V_{CC}$  applied to ORG input may increase the device Standby current).

Table 1

| Device | Number of Bits | Number of 8-Bits<br>Bytes | Number of 8-Bits<br>Words |

|--------|----------------|---------------------------|---------------------------|

| A93C46 | 1024           | 128                       | 64                        |

#### 2. Instructions

The A93C46 is accessed via a simple and versatile three-wire serial communication interface. Device operation is controlled by seven instructions issued by the Host processor. A valid instruction starts with a rising edge of CS and consists of a Start bit (SB), followed by the appropriate opcode, and the desired memory address location.

Table 2

|                         | Table 2                         |           |          |                        |       |                            |        |

|-------------------------|---------------------------------|-----------|----------|------------------------|-------|----------------------------|--------|

| Instruction Description |                                 | Start Op- |          | x8 Origination (ORG=0) |       | x16 Origination<br>(ORG=1) |        |

|                         |                                 | Bit       | Sit Code | Address (1)            | Data  | Address (1)                | Data   |

| READ                    | Read Data from Memory           | 1         | 10       | A6-A0                  | D7-D0 | A5-A0                      | D15-D0 |

| WRITE                   | Write Data from Memory          | 1         | 01       | A6-A0                  | D7-D0 | A5-A0                      | D15-D0 |

| EWEN                    | Write Enable                    | 1         | 00       | 11X XXXX               | -     | 11 XXXX                    | -      |

| EWDS                    | Write Disable                   | 1         | 00       | 00X XXXX               | -     | 00 XXXX                    | -      |

| ERASE                   | Erase Byte or Word              | 1         | 11       | A6-A0                  | -     | A5-A0                      | -      |

| ERAL                    | Erase all Memory                | 1         | 00       | 10X XXXX               | -     | 10 XXXX                    | -      |

| WRAL                    | Write all Memory with Same Data | 1         | 00       | 01X XXXX               | D7-D0 | 01 XXXX                    | D15-D0 |

(1) X = Don't Care bit

REV0.9 - AUG 2024 RELEASED - - 6 -

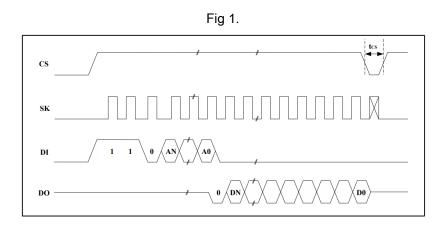

#### 3. Read

The Read Data from Memory (READ) instruction outputs data on Serial Data Output (DO). When the instruction is received, the op-code and address are decoded, and the data from the memory is transferred to an output shift register. A dummy 0 bit is output first, followed by the 8-bit byte or 16-bit word, with the most significant bit first. Output data changes are triggered by the rising edge of Serial Clock (SK). The A93C46 automatically increments the internal address register and clocks out the next byte (or word) as long as the Chip Select Input (CS) is held High. In this case, the dummy 0 bit is not output between bytes (or words) and a continuous stream of data can be read (the address counter automatically rolls over to 00h when the highest address is reached).

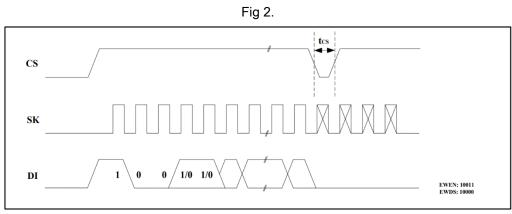

#### 4. Erase and Write Data

Write Enable and Write Disable: The Write Enable (EWEN) instruction enables the future execution of erase or write instructions, and the Write Disable (EWDS) instruction disables it. When power is first applied, the A93C46 initializes itself so that erase and write instructions are disabled. After a Write Enable (EWEN) instruction has been executed, erasing and writing remains enabled until a Write Disable (EWDS) instruction is executed, or until Vcc falls below the power-on reset threshold voltage. To protect the memory contents from accidental corruption, it is advisable to issue the Write Disable (EWDS) instruction after every write cycle. The Read Data from Memory (READ) instruction is not affected by the Write Enable (EWEN) or Write Disable (EWDS) instructions.

REV0.9 - AUG 2024 RELEASED - - 7 -

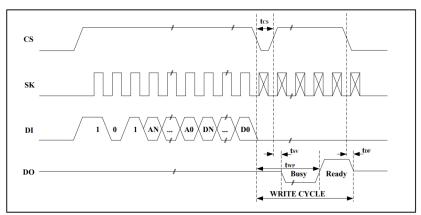

Write: For the Write Data to Memory (WRITE) instruction, 8 or 16 data bits follow the op-code and address bits. These form the byte or word that is to be written. As with the other bits, Serial Data Input (DI) is sampled on the rising edge of Serial Clock (SK). After the last data bit has been sampled, the Chip Select Input (CS) must be taken low before the next rising edge of Serial Clock (SK). If Chip Select Input (CS) is brought low before or after this specific time frame, the self-timed programming cycle will not be started, and the addressed location will not be programmed. The completion of the cycle can be detected by monitoring the READY/BUSY line, as described later in this document. Once the Write cycle has been started, it is internally self-timed (the external clock signal on Serial Clock (SK) may be stopped or left running after the start of a Write cycle). The Write cycle is automatically preceded by an Erase cycle, so it is unnecessary to execute an explicit erase instruction before a Write Data to Memory (WRITE) instruction.

Fig 3.

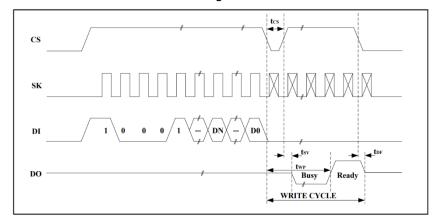

Write All: As with the Erase All Memory (ERAL) instruction, the format of the Write All Memory with same Data (WRAL) instruction requires that a dummy address be provided. As with the Write Data to Memory (WRITE) instruction, the format of the Write All Memory with same Data (WRAL) instruction requires that an 8-bit data byte, or 16-bit data word, be provided. When the ORG is valid, the two bytes of data should be the same. This value is written to all the addresses of the memory device. The completion of the cycle can be detected by monitoring the READY/BUSY line, as described next.

Fig 4.

REV0.9 - AUG 2024 RELEASED -

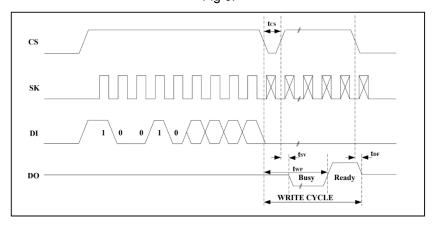

**Erase Byte or Word:** The Erase Byte or Word (ERASE) instruction sets the bits of the addressed memory byte (or word) to 1. Once the address has been correctly decoded, the falling edge of the Chip Select Input (CS) starts the self-timed Erase cycle. The completion of the cycle can be detected by monitoring the READY/BUSY line, as described in next Section: READY/BUSY status.

Fig 5.

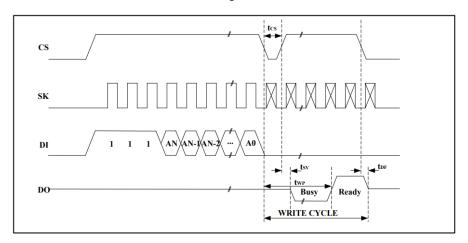

**Erase All:** The Erase All Memory (ERAL) instruction erases the whole memory (all memory bits are set to 1). The format of the instruction requires that a dummy address be provided. The Erase cycle is conducted in the same way as the Erase instruction (ERASE). The completion of the cycle can be detected by monitoring the READY/BUSY line, as described in next Section: READY/BUSY status.

Fig 6.

#### 5. READY/BUSY status

While the Write or Erase cycle is underway, for a WRITE, ERASE, WRAL or ERAL instruction, the Busy signal (DO=0) is returned whenever Chip Select input (CS) is driven high. (Please note, though, that there is an initial delay, of tcs, before this status information becomes available). In this state, the A93C46 ignores any data on the bus. When the Write cycle is completed, and Chip Select Input (CS) is driven high, the Ready signal (DO=1)

indicates that the A93C46 is ready to receive the next instruction. Serial Data Output (DO) remains set to 1 until the Chip Select Input (CS) is brought low or until a new start bit is decoded.

### 6. Initial Delivery State

The device is delivered with all bits in the memory array set to 1 (each byte contains FFh).

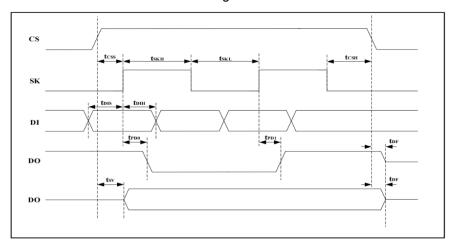

### 7. Synchronous Data Timing

Fig 7.

REV0.9 - AUG 2024 RELEASED - - 10 -

# **PACKAGE INFORMATION**

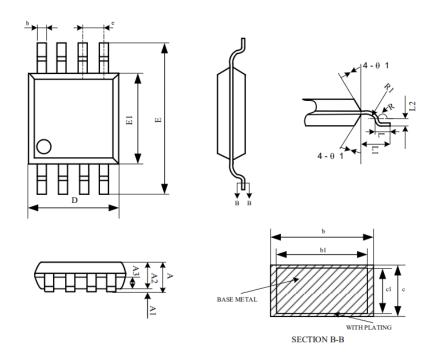

Dimension in SOP8 (Unit: mm)

| Symbol | Min       | Max   |  |  |

|--------|-----------|-------|--|--|

| А      | 1.350     | 1.750 |  |  |

| A1     | 0.100     | 0.230 |  |  |

| В      | 0.390     | 0.480 |  |  |

| С      | 0.210     | 0.260 |  |  |

| D      | 4.700     | 5.100 |  |  |

| E1     | 3.700     | 4.100 |  |  |

| Е      | 5.800     | 6.200 |  |  |

| е      | 1.270 BSC |       |  |  |

| L      | 0.500     | 0.800 |  |  |

| θ      | 0°        | 8°    |  |  |

REV0.9 - AUG 2024 RELEASED -

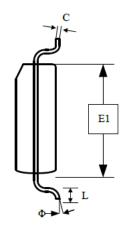

# Dimension in SSOP8 (Unit: mm)

| Symbol | Min   | Max   |

|--------|-------|-------|

| Α      | 1.000 | 1.300 |

| A1     | 0.000 | 0.100 |

| A2     | 1.000 | 1.200 |

| A3     | 0.370 | 0.470 |

| b      | 0.150 | 0.300 |

| b1     | 0.150 | 0.250 |

| С      | 0.110 | 0.200 |

| c1     | 0.110 | 0.160 |

| D      | 2.850 | 3.050 |

| E      | 3.950 | 4.250 |

| E1     | 2.700 | 2.900 |

| е      | 0.550 | 0.750 |

| L      | 0.200 | 0.600 |

| L1     | 0.650 | REF.  |

| L2     | 0.250 | BSC.  |

| R      | 0.050 | -     |

| R1     | 0.050 | -     |

| θ      | 0°    | 8°    |

| θ1     | 10°   | 14°   |

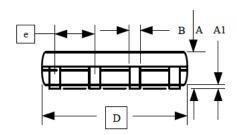

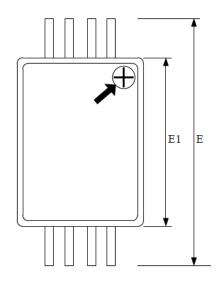

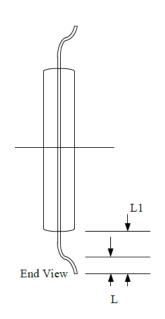

## Dimension in TSSOP8 Package (Unit: mm)

Top View

Side View

| Symbol | Min       | Max   |  |

|--------|-----------|-------|--|

| D      | 2.900     | 3.100 |  |

| Е      | 6.200     | 6.600 |  |

| E1     | 4.300     | 4.500 |  |

| Α      | -         | 1.200 |  |

| A1     | 0.050     | 0.150 |  |

| b      | 0.210     | 0.300 |  |

| е      | 0.650 BSC |       |  |

| L      | 0.450     | 0.750 |  |

| L1     | 1.000 REF |       |  |

REV0.9 - AUG 2024 RELEASED - - 13 -

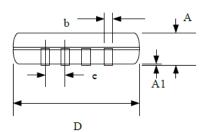

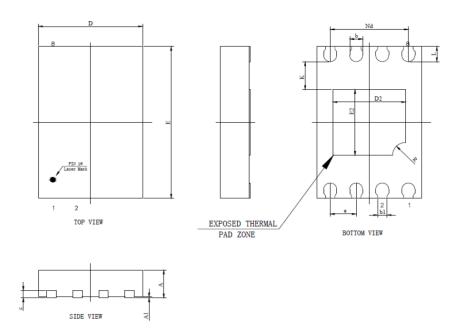

## Dimension in DFN8 (Unit: mm)

| Symbol | Min       | Max   |  |

|--------|-----------|-------|--|

| Α      | 0.500     | 0.600 |  |

| A1     | 0.000     | 0.050 |  |

| b      | 0.200     | 0.300 |  |

| b1     | 0.180     | REF.  |  |

| С      | 0.152     | REF   |  |

| D      | 1.900     | 2.100 |  |

| D2     | 1.300     | 1.500 |  |

| Е      | 2.900     | 3.100 |  |

| E2     | 1.200     | 1.400 |  |

| е      | 0.500     | BSC.  |  |

| Nd     | 1.500     | BSC.  |  |

| L      | 0.250     | 0.350 |  |

| R      | 0.200     | 0.300 |  |

| K      | 0.550 REF |       |  |

REV0.9 - AUG 2024 RELEASED - - 14 -

## **IMPORTANT NOTICE**

AiT Semiconductor Inc. (AiT) reserves the right to make changes to any its product, specifications, to discontinue any integrated circuit product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

AiT Semiconductor Inc.'s integrated circuit products are not designed, intended, authorized, or warranted to be suitable for use in life support applications, devices or systems or other critical applications. Use of AiT products in such applications is understood to be fully at the risk of the customer. As used herein may involve potential risks of death, personal injury, or serve property, or environmental damage. In order to minimize risks associated with the customer's applications, the customer should provide adequate design and operating safeguards.

AiT Semiconductor Inc. assumes to no liability to customer product design or application support. AiT warrants the performance of its products of the specifications applicable at the time of sale.

REV0.9 - AUG 2024 RELEASED - - 15 -